存储器概述 链接到标题

作用 链接到标题

- 存放数据和程序

- 计算机高速自动运行的基础

缺点 链接到标题

- 读取速度远远低于CPU的运行速度

- 冯.诺依曼的串行访问

设计目标 链接到标题

- 低成本

- 高速度

- 大容量

归纳起来是两个矛盾分别的平衡

- 速度和成本:存储器的速度越快,成本越高

- 容量和成本:存储器的容量越大,成本越高 对应的下面用两种方法区解决:

- 分层存储

- 虚拟存储器

实现方法 链接到标题

- 采用高速器件提高存取速度

- 改进组织形式(哈佛结构,分层结构)

存储器件的分类 链接到标题

存储器由存储介质和读写数据的控制部件组成。

按存储介质分类 链接到标题

大的可以分为三种:光、磁、半导体

半导体 链接到标题

- 易失性存储器(RAM):可以直接访问任何存储单元而不需要按照顺序

- 双极型TTL

- 存取速度快,

- 但集成度低,一般用于大型计算机或高速微机的Cache;

- MOS型

- (静态)SRAM:

- 速度较快,

- 集成度较低,

- 一般用于对速度要求高、而容量不大的场合(Cache)。

- (动态)DRAM:

- 集成度较高

- 但存取速度较低,

- 一般用于需较大容量的场合

- (主存): DDR, DR, CDRAM

- (静态)SRAM:

- 双极型TTL

- 非易失性存储器NVM

- 掩模ROM

- 一次性可编程PROM

- 可擦除可编程ROM(EPROM)

- 电可擦除可编程ROM(EEPROM)

- 闪存(Flash Memory)

磁存储器 链接到标题

磁带、软磁盘、硬磁盘

光存储器 链接到标题

只读型、一次可写型、多次可写型

读写策略分类 链接到标题

数据传送方式 链接到标题

- 并行存储器:IDE接口硬盘

- 串行存储器:U盘,SATA接口硬盘

数据存取(读写)顺序 链接到标题

- 随机存取(比如RAM)

- 顺序存取(比如磁带):先进先出

- 堆栈存储:先进后出

半导体存储芯片的基本结构与性能指标 链接到标题

注释

冯.诺依曼结构中的存储器是指现代计算机中的主存,磁盘和光盘属于输入输出设备

随机存取存储器 链接到标题

存储单元———单管DRAM:集成度高,但速度较慢,价格低,一般用作主存

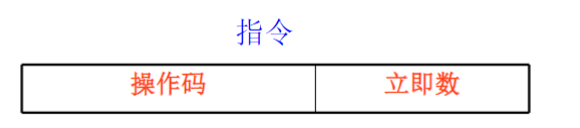

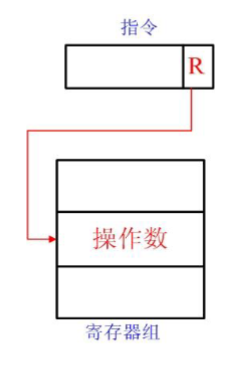

单译码 链接到标题

就是数电当时学过的行选信号以及列选信号,

- 地址线 m 根,数据线 N 根; 地址线m与存储单元列的关系为 $$ M=2^m $$

双译码 链接到标题

- 地址线 2n 根,数据线 1 根

- 基本存储单元排列成N*N的正方矩阵,且有N=2n, $$M=N×N=2^{2n}$$

优缺点 链接到标题

- 单译码

- 优点:译码电路结构简单

- 缺点:当字数大大超过位数时,存储器芯片会形成纵向很长而横向很窄的不合理结构只适用于构建容量不大的存储器

注释

- 字数对应的是地址线,

- 位数对应的是数据线

- 双译码

- 优点:可以有效减少片内选择线数目和驱动器数目,适 用于构建容量大的存储器

- 缺点:译码电路结构较复杂

只读存储器ROM 链接到标题

| 序号 | 类型 | 写入方式 | 擦除方式 | 擦除大小 |

|---|---|---|---|---|

| 1 | 掩膜式 ROM | 工厂里用特殊的方法烧录 | 写入后无法修改 | ——- |

| 2 | PROM | 专用的编程器,只能写入一次 | 写入后无法修改 | ——- |

| 3 | EPROM | 专用的编程器 | 专用紫外线擦除器,擦除时间长(数十分钟) | 整个芯片 |

| 4 | E²PROM | 在线读写,集成度较低,存取速度较慢,次数有限 | 电子信号修改 | 字节 |

| 5 | Flash | 在线读写,集成度高,高速存取,重复改写次数多 | 电子信号修改 | 部分或整个芯片 |

主要技术指标 链接到标题

也就是选择合理的芯片:

- 价格

- 存储容量:N×M

- 但各个存储芯片的存取速度

- 存取时间

- 存取周期

- 数据传输速率

- 功耗(mW/芯片或者$\mu$W/芯片)

- 可靠性:平均故障间隔

- 工作电源电压、工作温度范围、可编程存储器的编程次数、 成本

- 整个存储器速度指标:带宽(b/s或B/s)

两种优化措施 链接到标题

分别用于解决两个矛盾。

存储器的层次结构 链接到标题

解决存储器速度和成本的矛盾

- 设计目标:整个存储系统速度接近M1,而价格和容量接近Mn

- 原因:存储器访问的局部性

- 操作策略:

- 映像规则:

- 查找规则

- 替换规则

- 更新规则

虚拟存储器与地址映射 链接到标题

信息

虚拟内存技术就是自动执行程序覆盖段的技术

分页 链接到标题

- 页是信息的物理单位,与源程序的逻辑结构无关

- 页长由系统确定,大小固定,用户不可见

- 页面只能以页大小的整倍数地址开始

分段 链接到标题

- 段是信息的逻辑单位,由源程序的逻辑结构所决定

- 段长由用户确定(用户可见),大小不固定

- 段可以从任意地址开始,段内连续编址,段间不一定连续

现代计算机的多层次储存体系 链接到标题

四个层次

- CPU寄存器:正在执行的指令和数据

- Cache:指令和数据的高速本地暂时存储副本

- 主存:存放运行中的程序和数据

- 辅存:存放不活动的程序和数据

cache读取方式 链接到标题

设cache 的存取时间为$t_c$,命中率为$h$,主存的存取时间为$t_m$,则平均存取时间:

- 贯穿式:$$t_a=t_c h+(t_c+t_m)(1-h)$$

- 旁路式:$$t_a=t_c h+t_m(1-h)$$

旁路式是CPU与cache和主存都有连接。

A[数据源] --> B[缓冲区/Cache] B --> C[处理单元] C --> D[读取输出] style A fill:#f9f,stroke:#333,stroke-width:2px style B fill:#bbf,stroke:#333,stroke-width:2px style C fill:#bfb,stroke:#333,stroke-width:2px style D fill:#fbb,stroke:#333,stroke-width:2px

cache技术和虚拟存储器技术的比较 链接到标题

相同 链接到标题

- 以存储器访问的局部性为基础

- 采用的调度策略类似

- 对用户都是透明的

不同点: 链接到标题

- 划分的信息块的长度不同

- Cache技术由硬件实现,而虚拟存储器由OS的存储管理软件辅助硬件 实现

- Cache技术解决处理成本和速度问题,虚拟存储器技术解决成本和容 量问题

主存储器特点 链接到标题

- 最小可编址单位为字节,但一般按字长进行访问

- 主存储器用于存放当前运行的程序和数据

- 长度大于一个字节的数据在内存占多个连续的单元,根据字节存放顺序(字节序)分为大端和小端

- 为了提高访问速度,一般按整数边界对齐存储

- 注意主存大小与CPU的访存空间的区别

主存储器设计技术 链接到标题

存储芯片的选型 链接到标题

- 类型

- 型号以及数量 原则应该是种类和数

存储芯片的组织形式 链接到标题

模块结构—存储芯片互连 链接到标题

其实就是数电的知识,我觉得ppt中给的图非常的直观。

- 位扩展:地址线和控制线互连、数据线并列(扩展数据位数)

- 字扩展:地址线、控制线和数据线互连(扩展地址线)

- 混合扩展 在互联的时候将高位经过译码器后作为芯片的位选信号。

地址译码技术 链接到标题

固定地址译码 链接到标题

- 全译码:所有未参与字选的高位地址线全部参与译码形成片选信号

- 部分译码:只有部分高位地址线参与译码形成片选信号

- 线译码:用单独的高位地址线作为片选信号